India Banned Foreign Drones But Still Imports 45-55% of Critical Components—Here’s Why

India's 2022 drone import ban aimed for self-reliance. Reality: 45-55% of flight controllers, motors, sensors still imported. Deep localization takes years

India's 2022 drone import ban aimed for self-reliance. Reality: 45-55% of flight controllers, motors, sensors still imported. Deep localization takes years

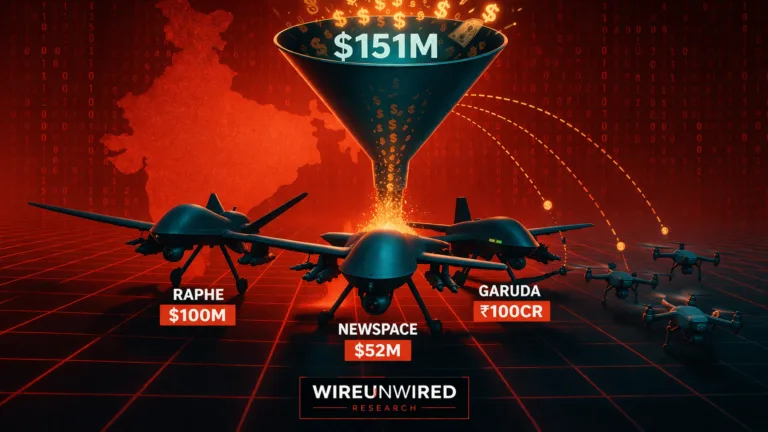

$151M raised by Indian drone startups, but Raphe ($100M), NewSpace ($52M), Garuda (₹100cr) captured majority. Defense dominates funding while civil apps struggle.

"BSF seized 272 drones, 367kg heroin along Punjab border in 2025. Jammu attack showed military vulnerability. Counter-drone authorization gaps remain.

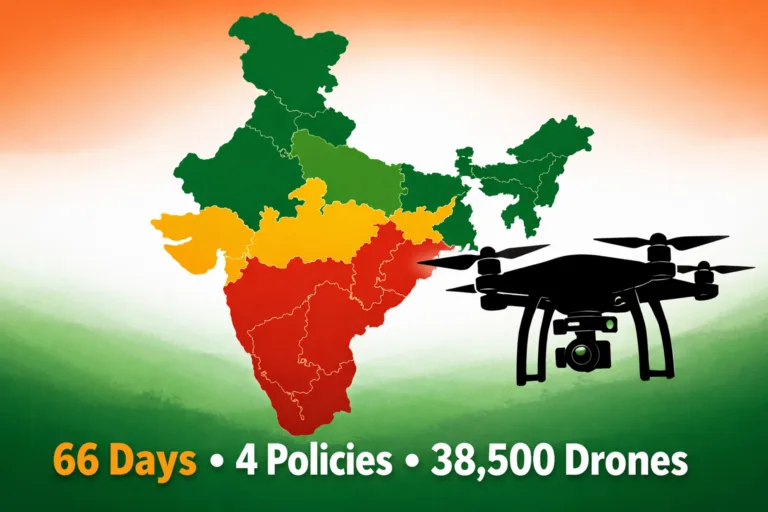

India built a functional drone industry in five years through a regulatory strategy that’s rare in government. From ripping up the permission-heavy regime, replacing it with a digital platform, zone the entire country’s airspace in three colors, ban foreign competition,…

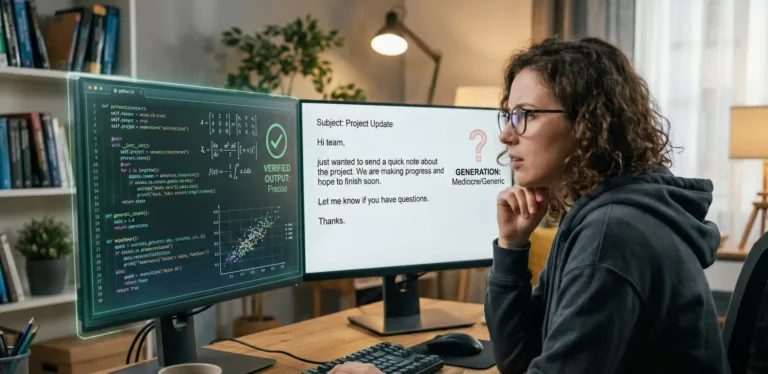

Discover why LLMs like ChatGPT nail complex code and math but produce generic emails and essays. It's not a bug—it's the lack of verifiable feedback. Explore the RLHF gap driving AI's uneven progress

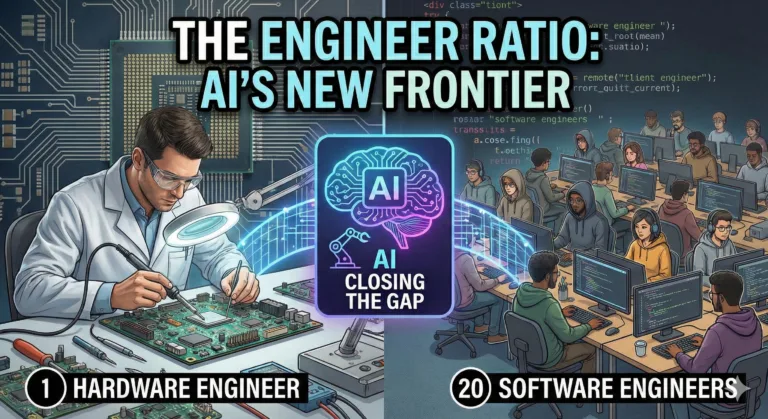

20 software engineers exist for every hardware engineer in the US. AI tools are turning software talent into chip designers—but senior expertise still wins

OpenAI Syndrome hits Microsoft, AMD, Oracle: Strong AI earnings, crashing stocks. MOUs fail to deliver contracts, sparking debt fears & overcapacity risks.

Discover how macOS Quality of Service (QoS) uses Efficiency cores to deliver 12+ hours of battery life. Learn why Apple Silicon outlasts Intel by design.

C2PA to label AI images is failing. Platforms strip metadata, Apple won't join, creators reject labels. Instagram says assume photos aren't real.

Security researcher found RCE in AMD AutoUpdate affecting millions. AMD closed report same day as 'out of scope,' refuses to fix HTTP download flaw.

Ex-Google engineer convicted for stealing AI secrets faces 70 years. Mirrors Taiwan's TSMC case—AI now treated as national security threat, not just IP.

FPT reveals Vietnam's first fully Vietnamese-owned advanced semiconductor testing plant in Hanoi. As global chip tensions rise, this could produce billions of units yearly—but can it rival Taiwan? (148 characters)

RISC-V's customizable design enables innovation but makes verification impossible. Testing trillions of instruction combos risks fragmentation. Read to know more

LLMs choke on million-token contexts, but recursion changes that. Prime Intellect's RLM spawns sub-models to surgically dissect data.

China's Shenzhen EUV prototype is live, torching U.S. chip controls and splitting the $600B market into rival empires. Independence by 2028 means game over for global unity.

ASML fires 1700 mostly managers amid €13.2B Q4 bookings surge from AI boom. Why trim leadership now as chip demand explodes? Streamlining risks execution amid TSMC, Samsung rush. (148 characters)

Apple turns to Intel's 14A process for non-Pro iPhone chips starting 2028, diversifying from TSMC amid capacity strains. As AI demand surges, this supply shift exposes risks in the chip foundry race—leaving premium silicon exclusive.

The era of 'Assembled in India' is ending. The era of 'Owned by India' has begun. From Lava's UK launch to Tata's new fabs, we connect the dots on the 18-month roadmap to Hardware Sovereignty.

For 20 years, the iPhone dictated TSMC's roadmap. That era is over. We analyze the "Revenue Density" math that explains why TSMC is pivoting $56B in Capex toward NVIDIA, leaving smartphone giants to pay the bill.

Apple has secured 100% of TSMC's 2nm capacity, marking the end of the 15-year FinFET era. We analyze why the transistor's shape had to change to Gate-All-Around (GAA).