Imagine we’re sitting down to review your architecture for a new satellite project, and you ask me a perfectly logical question: “Can I just drop in my standard IP cores for this space FPGA?”

My short answer will be: No. Down here on Earth, we are spoiled. We use familiar Intellectual Property (IP) cores—DDR controllers, high-speed interfaces, processors, and communication blocks—and they work beautifully. But when you launch that FPGA into orbit, the environment drastically changes. There is nothing normal to be so sure about and suddenly your trusted IP becomes your biggest liability.

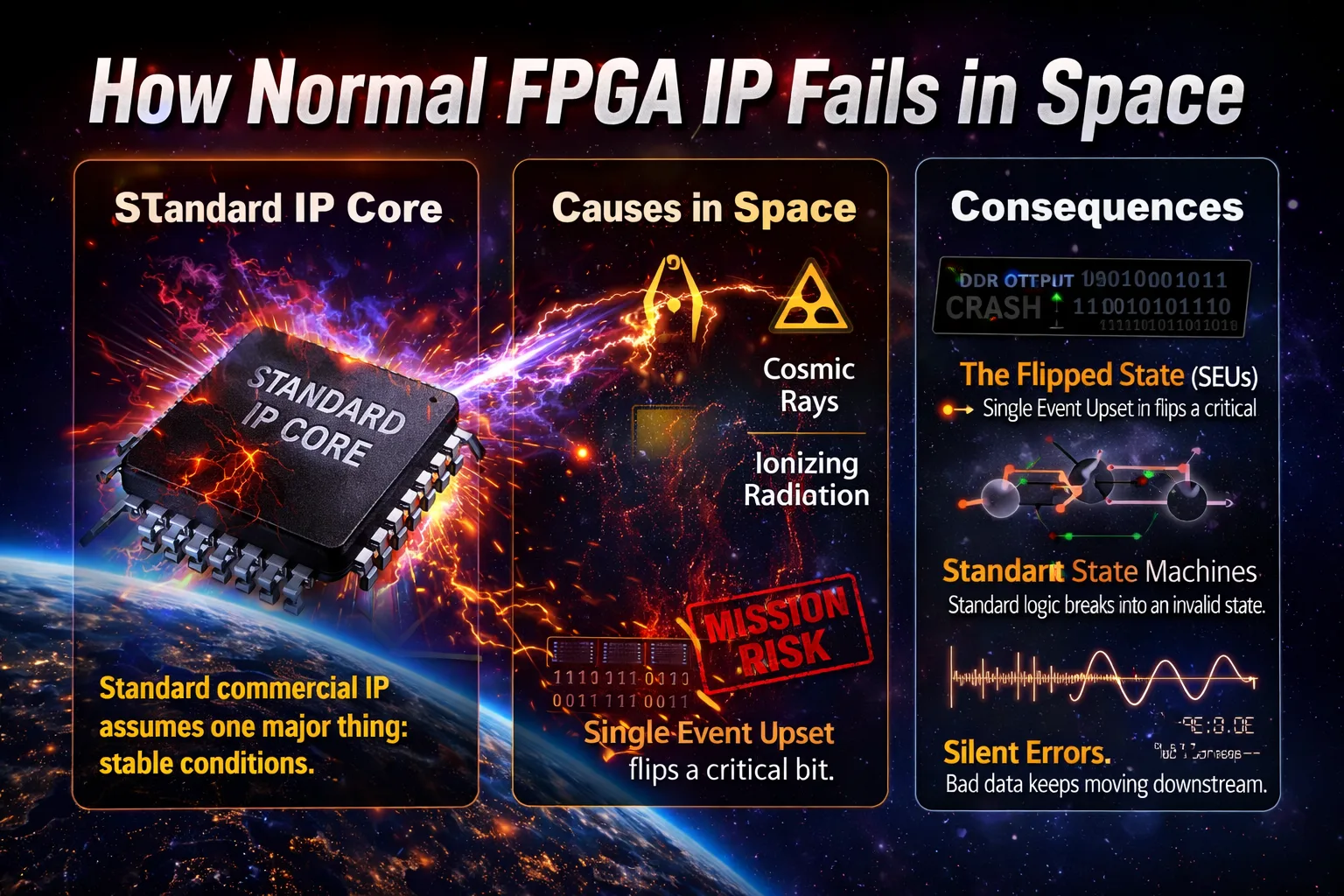

How Normal FPGA IP Fails in the Space ?

Standard commercial IP assumes one major thing: stable conditions. It trusts that if it stores a 0 in a register, that register will hold a 0 until told otherwise. Space is anything but stable.

When your FPGA is in orbit, it is constantly bombarded by high-energy particles and ionizing radiation. Here is exactly what goes wrong when one of those particles strikes a standard IP core:

The Flipped State (SEUs): A cosmic ray hits a transistor and flips a bit from a

0to a1(a Single Event Upset). If this happens in a data payload, you get a bad pixel in an image. If this happens in the control register of your standard DDR controller, the entire memory interface might crash.Broken State Machines: Standard state machines don’t know what to do if they are suddenly forced into an undefined state. They will either lock up indefinitely, loop endlessly, or do something completely erratic.

Silent Errors: Without constant self-checking, a corrupted data path will just keep passing bad data downstream. Your system will think it’s working perfectly while sending garbage telemetry back to Earth.

Normal IP just isn’t built to expect the universe to actively sabotage it.

Nine FPGA ML Accelerator Mistakes That Kill Real-World Performance

How are Space ready IP Different ?

To survive in space, IP selection isn’t a plug-and-play exercise; it is a critical risk decision. Space-ready IP expects things to break and is designed around these five pillars:

1. Built-in Fault Tolerance

Space IP doesn’t trust a single point of failure. It uses techniques like TMR (Triple Modular Redundancy) in its critical paths. This means it computes the same thing three times and holds a “vote.” If a radiation strike flips one bit, the other two outvote it, and the system keeps running smoothly. It also relies heavily on protected state machines and strict error detection logic.

2. Actual Recovery Mechanisms

It’s not enough to just flag that an error happened. What do you do next? Good space IP actively recovers. It incorporates automatic resets for corrupted blocks, reinitializes stalled interfaces, and executes safe, predictable restart sequences without needing ground control to intervene.

3. Ironclad Data Integrity

Memory and data paths must be guarded at all times. Space IP relies heavily on Error Correcting Codes (ECC), parity checks, and constant integrity validation. This is what stops those terrifying “silent” corruptions from ruining your mission data.

4. Deterministic Behavior

Space systems demand predictability. When an error occurs, the IP must fail predictably and avoid undefined states, hidden dependencies, or random lockups. You need to know exactly how the core will behave under stress.

5. Validation Under Single Event Effects (SEE)

This is where I see a lot of engineering teams fail. You can simulate the IP on Earth, and you can test it in standard hardware. But if you haven’t validated it under radiation, you are flying blind. To fix this, you have to run fault injection at the RTL and system levels, use actual radiation test data, and validate the recovery behavior, not just the detection.

You Would Love To Read : Why Most FPGA Engineers Are Over 30: Inside a Niche Tech Career

The Real Mistake Teams Make

The biggest trap in aerospace FPGA design is the assumption that “IP is a solved problem.” It isn’t. Every time you integrate an IP block into a space project, you must interrogate it. You have to ask:

Is this IP inherently fault-tolerant?

What exactly happens when an error occurs?

Can it recover safely without bricking the system?

Has it actually been validated for harsh radiation environments?

If you don’t test for SEE, you simply do not know how your design will behave in space.

Discover more from WireUnwired Research

Subscribe to get the latest posts sent to your email.