Verilog Vs SystemVerilog :What should I learn first is a common question among hardware engineers and VLSI designers. Well ,the answer completely depends upon your goals, background, and the industry you want to work in.

In this article I will try you to give a clear picture of what should you learn first Verilog or SystemVerilog, depending upon your goals and targets.

Prerequisite: You must know what your interests are , and where do you want yourself in your professional career.

🔹 1. Understanding the Differences between Verilog and SystemVerilog

| Feature | Verilog | SystemVerilog |

|---|---|---|

| Type | Hardware Description Language (HDL) | HDL + Hardware Verification Language (HVL) |

| Purpose | Used for RTL design (register-transfer level modeling) | Used for both RTL design and verification |

| Data Types | Supports only reg, wire, and integer types | Rich data types (bit, logic, struct, enum, class, etc.) |

| Concurrency | Uses procedural and continuous assignments | Adds new concurrency features like fork-join |

| Testbench Support | Requires manual testbenches | Provides Object-Oriented Programming (OOP), constraint, randomization, and interfaces |

| Assertions | Not available | Includes SystemVerilog Assertions (SVA) for verification |

| Interfaces | Uses simple wire connections | Supports interface and modport for better connectivity |

Also Read :Understanding the automatic Keyword in SystemVerilog: The Key to Proper Recursion

🔹 2. Who Should Learn What First?

| Your Goal | Start with Verilog? | Start with SystemVerilog? |

|---|---|---|

| RTL Design (ASIC/FPGA) | ✅ Yes | Optional |

| Verification Engineer (UVM/OVM) | ❌ Not necessary | ✅ Yes |

| Beginners in Digital Design | ✅ Yes | ❌ No, too complex |

| Industry/Company Requirement | ✅ Yes (ASIC/FPGA focus) | ✅ Yes (Verification focus) |

Also Read :Digital Electronics for Placements – A Step-by-Step Guide

🔹 3. Learning Path: What Should You Learn First :Verilog Vs SystemVerilog?

✅ Start with Verilog if:

✔️ You are new to hardware design and want to understand digital logic.

✔️ You plan to work on FPGA or ASIC design (RTL coding).

✔️ You need to write synthesizable code for implementation.

🚀 Move to SystemVerilog if:

✔️ You already know basic Verilog and want to improve productivity.

✔️ You are moving into Verification (UVM/OVM, assertions, testbenches).

✔️ You want to work with advanced verification methodologies (randomization, OOP, assertions, functional coverage).

TRENDING

🔹 4. A Step-by-Step Approach towards Learning

📌 Step 1: Learn Verilog (2-3 Months)

- Basic digital design concepts (Combinational & Sequential Circuits)

- Verilog module, always blocks, blocking vs non-blocking

- FSM (Finite State Machines) and basic testbenches

- Synthesizable vs Non-synthesizable constructs

📌 Step 2: Learn SystemVerilog (3-4 Months)

- Data types:

bit,logic,struct,enum,class - Object-Oriented Programming (OOP)

- Interfaces & Modports

- Randomization & Constraints

- Assertions (SVA)

- Coverage-driven verification

🔹 5. What the Industry Prefers between Verilog and SystemVerilog ?

🔹 FPGA & ASIC Design Engineers → Verilog first, then SystemVerilog for efficiency

🔹 Verification Engineers (UVM, OVM) → SystemVerilog first, then UVM for testbenches.

🎯 Final Verdict: Verilog vs. SystemVerilog

💡 If you’re a beginner in RTL design → Start with Verilog, then move to SystemVerilog.

💡 If you want to work in verification → SystemVerilog (UVM) is a must, but basic Verilog knowledge helps.

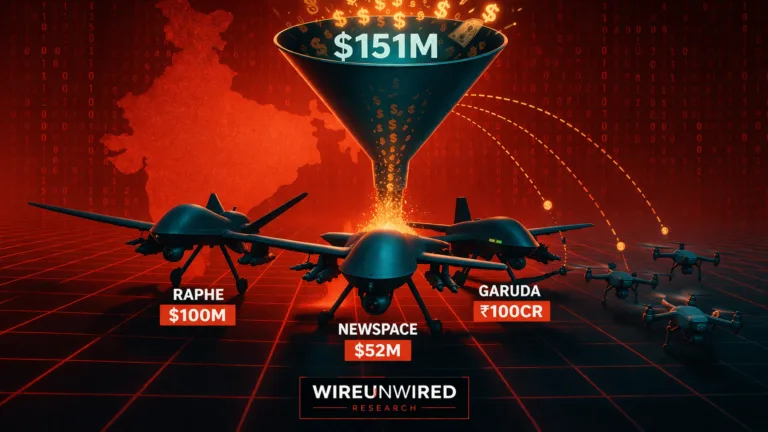

Discover more from WireUnwired Research

Subscribe to get the latest posts sent to your email.